Agilent E2925B Opt. 200 PCI Performance Optimizer

## **User's Guide**

### **Important Notice**

This document contains propriety information that is protected by copyright. All rights are reserved. Neither the documentation nor software may be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form, in whole or in part, without the prior written consent of Agilent Technologies.

© Copyright 1998, 2000 by: Agilent Technologies Herrenberger Straße 130 D-71034 Böblingen Germany

The information in this manual is subject to change without notice. Agilent Technologies makes no warranty of any kind with regard to this manual, including but not limited to the implied warranties of merchantability and fitness for a particular purpose.

Agilent Technologies shall not be liable for errors contained herein or direct, indirect, special, incidental, or consequential damages in connection with the furnishing, performance, or use of this manual.

Brand or product names are trademarks or registered trademarks of their respective companies or organizations.

Authors: Stephan Greisinger and Stefan Kunzi, t3 medien GmbH

## Contents

| PCI Performance Optimizer Overview |                                 | 7  |

|------------------------------------|---------------------------------|----|

| The Process of PCI                 | Design                          | ç  |

| The Approach of th                 | e Performance Optimizer         | 10 |

| Measuring the Sy                   | stem Performance in Real Time   | 11 |

| Using Post-Proce                   | ssed Analysis                   | 11 |

| Selecting the App                  | propriate Way of Analysis       | 13 |

| The PCI Performan                  | ce Optimizer's User Interface   | 14 |

| Rules for Proper PC                | CI Design                       | 16 |

| Running a Sample PCI Performar     | nce Optimizer Session           | 17 |

| Determining the Ov                 | verall System Performance       | 19 |

| Analyzing the Perfo                | ormance of the PCI Host Bridge  | 21 |

| Loading the Setup                  | o File                          | 21 |

| Setting up the Me                  |                                 | 22 |

| Specifying the Ma                  | aster and Target Identification | 22 |

| Specifying the Da                  | ita Capture                     | 24 |

| Viewing the Test I                 | Results                         | 25 |

| Setting Up a PCI Performance Op    | otimizer Test                   | 29 |

| Setting Up the Test                | Hardware                        | 31 |

| Master Identifica                  | tion                            | 32 |

| Target Identificati                | on                              | 33 |

| Preparing the Softv                | vare for the Test               | 33 |

| Enabling the PCI F                 | Performance Optimizer           | 34 |

| Setting Up the Re                  | port                            | 35 |

| Setting up the Tar                 | get Identification              | 36 |

| Setting up the Ma                  | ster Identification             | 37 |

| Selecting a Maste                  | er/Target Pair                  | 38 |

| Setting Up the Da                  | ta Capture                      | 38 |

| Measuring System or Device Performance |                                                   |    |

|----------------------------------------|---------------------------------------------------|----|

| Rur                                    | nning the Performance Measurements                | 43 |

| Inte                                   | erpreting the Result Charts                       | 44 |

|                                        | PCI Usage Tab                                     | 45 |

|                                        | Burst Usage Tab                                   | 46 |

|                                        | Command Tab                                       | 47 |

|                                        | Latency Tab                                       | 48 |

|                                        | Full Transaction Clocks Tab                       | 49 |

| Inte                                   | erpreting the Report Output                       | 50 |

| Usi                                    | ng the Report Output for Performance Evaluation   | 51 |

|                                        | General Information on the System under Test      | 51 |

|                                        | Analyzing the PCI Throughput                      | 52 |

|                                        | Analyzing the PCI Utilization                     | 52 |

|                                        | Analyzing the PCI Efficiency                      | 53 |

|                                        | The Bus Users Overview                            | 55 |

|                                        | Summary for the Performance Evaluation Example    | 55 |

| Usi                                    | ng the Report Output for Performance Optimization | 56 |

|                                        | Analyzing the Bus Utilization                     | 56 |

|                                        | Analyzing the Traffic Overhead                    | 57 |

|                                        | Analyzing the Wait States                         | 58 |

|                                        | Analyzing the Byte Enable and Burst Behavior      | 58 |

|                                        | Analyzing the Bursts                              | 59 |

|                                        | Analyzing Command Termination                     | 61 |

|                                        | Summary of the Performance Optimization Example   | 63 |

| Re-Using the Test Se                   | tups and Results                                  | 65 |

| Prir                                   | nting and Exporting Test Results                  | 67 |

|                                        | Printing the Test Results                         | 67 |

|                                        | Exporting the Report                              | 68 |

|                                        | Exporting the Trace Memory                        | 68 |

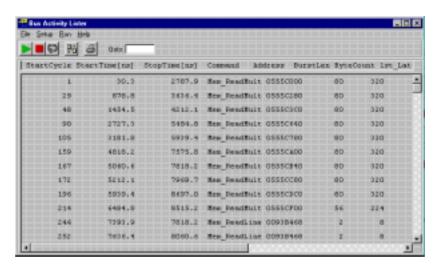

|                                        | Exporting the Bus Activity Listing                | 69 |

|                                        | Exporting the Test Settings                       | 69 |

| Re-                                    | Using Previously Saved Data                       | 70 |

| Going Further Into Details |                                                        |     |

|----------------------------|--------------------------------------------------------|-----|

|                            | Verifying Good Performance                             | 75  |

|                            | Performance in the Presented Charts                    | 75  |

|                            | Identifying Design Rule Violations                     | 76  |

|                            | Replacing Cards or Improving Behavior                  | 77  |

|                            | Improving Target Behavior                              | 78  |

|                            | Minimize Latencies                                     | 78  |

|                            | Command Termination                                    | 79  |

|                            | Using the Bus Activity Lister                          | 82  |

| Report Reference           |                                                        | 85  |

|                            | Example Transfers                                      | 87  |

|                            | Bus Statistics (Report Sections 1 to 7)                | 88  |

|                            | General Information (Report Section 1)                 | 88  |

|                            | Basic Bus Statistics (Report Section 2)                | 90  |

|                            | Bus Throughput Statistics (Report Section 3)           | 91  |

|                            | Efficiency Statistics (Report Section 4)               | 91  |

|                            | Bus Utilization Statistics (Report Section 5)          | 93  |

|                            | Bus Users Overview (Report Section 6)                  | 94  |

|                            | Interrupt Latency (Report Section 7)                   | 95  |

|                            | Master-Target Pair Measurements (Report Section 8)     | 96  |

|                            | The Header of Report Section 8                         | 96  |

|                            | Statistical Basis (Report Subsection 8.1)              | 97  |

|                            | Bus Usage (Report Subsection 8.2)                      | 97  |

|                            | Bus Utilization (Report Subsection 8.3)                | 98  |

|                            | Data Phase (Report Subsection 8.3.1)                   | 99  |

|                            | Time Overhead (Report Subsection 8.3.2)                | 101 |

|                            | Command Usage (Report Subsection 8.3.3)                | 102 |

|                            | Command Termination (Report Subsection 8.3.4)          | 104 |

|                            | Wait Histogram (Report Subsection 8.3.5)               | 105 |

|                            | Burst Length over Command (Report Subsection 8.3.6)    | 106 |

|                            | Efficiency Statistics (Report Subsection 8.4)          | 107 |

|                            | Efficiency over Burst Length (Report Subsection 8.4.1) | 108 |

|                            | Termination Statistics (Report Subsection 8.5)         | 109 |

|                            | Termination Burst Histogram (Report Subsection 8.5.1)  | 110 |

### Contents

|                       | Latency Histogram (Report Subsection 8.6) Top Ten List of First Word Latencies with Retries | 111 |

|-----------------------|---------------------------------------------------------------------------------------------|-----|

|                       | (Report Subsection 8.6.1)                                                                   | 113 |

| Definitions of Used I | Measures                                                                                    | 115 |

# PCI Performance Optimizer Overview

The Agilent E2925B Opt. 200 PCI Performance Optimizer is an additional option available for the Agilent E2920 verification tools series. Being fully integrated into the framework, it is employed together with a PCI Exerciser and Analyzer testcard and its graphical user interface (GUI).

The Performance Optimizer provides all features that are needed to evaluate and optimize any device under test in terms of the performance. This includes the devices on the PCI bus as well as the complete PCI system. For this purpose, the software defines and calculates performance measures as efficiency, data throughput, or bus utilization, that allow you to compare and communicate the test results.

With these features, you can easily reveal which devices cause poor performance in the system under test. Furthermore, you can examine the data traffic of every device in detail to track down the exact cause for the bad performance.

With this information provided by the software you can improve your system either by selecting components with better performance or by debugging or redesigning the affected devices.

## The Process of PCI Design

When the PCI technology was introduced in the PC environment, it was a lot faster than previously used buses (ISA, EISA). Initially, there was no need to optimize the performance of the PCI bus. This has changed by the time the requirement for fast data traffic has increased. Now the PCI bus often is the performance bottleneck, especially in high-performance servers that deal with lots of disk and network traffic. Due to the complex protocol there are many ways to improve PCI performance both on a component level as well as on a system level.

A huge number of companies and people develop chipsets, devices and systems using the PCI technology for data exchange. Even when obeying all the rules included in the PCI specification, the performance of your device still depends on many factors.

Possible scenarios within the process of PCI design are:

- you are designing a chip or an add-in card,

- you are integrating a system and you need to select between different components on the market,

- you are adjusting system and device parameters in order to optimize the overall performance.

For all imaginable tasks it is essential to evaluate the quality of the different devices in your system under test. Furthermore, it is important to document your results and to communicate them to colleagues or other companies.

These facts raise the question for a powerful, yet easy-to-use solution to find the bottlenecks in your system. If you manage to identify the part that decreases the system performance due to its poor design, you know what to improve or replace. Eventually, this process will lead to significantly more powerful PCI systems.

# The Approach of the Performance Optimizer

The Agilent E2925B Performance Optimizer provides all features needed to evaluate and optimize any PCI device or system. The test results presented by this software can be used to compare different devices or different combinations of devices. With this tool you gain all information required to improve the performance, either by selecting the best components or by optimizing the communication abilities of particular PCI devices.

The Methods for Performance

Analysis

Basically, there are two different approaches to analyze a system under test. It depends on the particular case which of the options is to be preferred. With the Agilent E2925B Performance Optimizer you can employ both methods for performance analysis:

- Real-Time Measurements (part of the PCI Analyzer)

Real-time performance analysis based on programmable counters allows long-termed observation of the system's properties like latencies, etc. This method provides valuable information over long time periods about what the general performance of your system is. It is limited, however, in its ability to provide meaningful insight to track down the root cause of performance issues.

- Post-Processed Analysis (with the PCI Performance Optimizer only) The post-processed analysis is based on one or more recorded traffic traces in the trace memory. This allows a detailed analysis of all performance aspects like bus utilization, command usage, burst efficiency, or wait histograms. This applies for the whole bus as well as for specific devices or a master/target pair. This information helps you to quickly determine why your performance problems may exist by allowing you to identify poorly performing PCI devices, drivers, or mismatched master/target pairs.

The trace memory of the Agilent E2925B testcard can store up to 64 k traffic samples. One sample here is referred to as a sequence of clock cycles without any changes in the bits that are significant for the performance. In order to base the calculations on a larger amount of traffic data for more reliable results, the Agilent E2995A 155 x 4 M Trace Memory Board can be employed, which can store up to 4 M traffic samples.

# Measuring the System Performance in Real Time

When using the real-time measurement options with the Performance Optimizer, your system under test can be observed over a long time. However, only a few different measures can be taken simultaneously. The software provides some pre-defined measures, but the internal performance counters can be freely programmed to match your personal needs.

The Display Options

The results of the real-time measurements can be monitored online. They are displayed on the screen while the measurements are running. The user can switch between two display modes:

- loadmeter display

The specified measures are displayed in a bar diagram.

- line diagram

The last 100 values are displayed in a line diagram over time.

The performance counters accumulate the specified bus events during an arbitrary measurement interval. The user can choose to either display the accumulated values or to reset the counters after each interval.

The real-time measurement options do not require the Performance Optimizer to be licensed for your software package. However, for completeness they are included in the Performance menu, too, because they provide important features for performance evaluation.

For a complete description of all features of the real-time measurements, please refer to *Analyzing PCI Performance* in the "*Agilent E2925B PCI Analyzer User's Guide*".

## **Using Post-Processed Analysis**

With the use of the post-processed analysis many different measures can be considered simultaneously. This allows a very detailed analysis of the data traffic on the bus. The observation time, however, is limited due to the large amount of data that is stored.

**Recording Traffic Samples**

The traffic is recorded in the trace memory of the Exerciser and Analyzer card. A set of values in the trace memory is referred to as a traffic sample. One traffic sample can be recorded for every clock cycle. However, if a sequence of clock cycles occurs on the bus without any changes in the relevant bits, like idle states, they are stored as one sample. This behavior extends the possible observation time and, thus, yields better measurement results based on a larger statistical base.

**Trace Memory Size**

The trace memory can store up to 64~k samples. For a larger trace memory, the Agilent E2995A 155~x~4~M Trace Memory Board is available. With this option you can record up to 4~M samples.

The Steps of Performance Optimization The Agilent E2925B PCI Performance Optimizer performs the data analysis by taking the following steps:

### • Recording the bus traffic

The measurement is either started by the user or can be set up to be triggered on a certain event occurring on the bus. Then the trace memory records the data until the trace memory is full or another specified bus event occurred on the bus.

Usually, the observation time is only a split of a second. Thus, the memory content is a "snapshot" of the bus activities.

### • Analyzing the recorded data

For the analysis, the trace memory content is loaded from the testcard into the PCI Performance Optimizer. The software then derives a large number of result values from the sampled bus activities.

### • Presenting the test results

The Performance Optimizer outputs the results of the analysis in graphical charts and in a textual report. This report is arranged according to the requirements of system and device evaluation and optimization. Several results are also presented in diagrams, histograms and tables.

These test results give a deep insight into your system's and devices' traffic behavior. You can identify the devices with poor performance and get detailed hints for improvement.

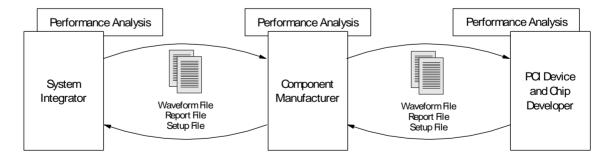

Providing result files (setup file, report file, and waveform file)

Optionally, you can store your test settings and test results in files.

With these files you can re-use the settings or the data from previous settings. They are also a convenient basis for communication between several user groups. The report file holds the results of the post-processed analysis in textual form, the waveform file holds the trace memory contents. The setup file with the test settings can be used to reproduce the test environment.

## **Selecting the Appropriate Way of Analysis**

The two available test methods—post-processed analysis and real-time measurements—are used for different tasks.

The following table gives an overview of the advantages and drawbacks of both methods:

|            | Real-Time Measurement                    | Post-Processed Analysis                 |

|------------|------------------------------------------|-----------------------------------------|

| Advantages | long observation time                    | many measures simultaneously            |

|            | good base for statistical considerations | very detailed analysis                  |

|            | trend control                            | re-usable results                       |

| Drawbacks  | only few measurements at the same time   | short observation time (snapshot)       |

|            |                                          | risk to measure non-representative data |

Both methods complement one another when used simultaneously. Starting the capture for post-processed analysis in an unfavorable moment during the benchmark may result in capturing data useless for the analysis. Monitoring the bus traffic with the real-time measurements while taking the snapshot for the post-processed analysis ensures that the snapshot contains representative data.

For example, when running a video game as benchmark to stress the PCI interface of a graphics card, this game could stop transferring video data just the moment you start the capture for post-processed analysis (perhaps because it is interrupted by something). Then you will probably observe that the PCI bus is idle through most of the observation time. To avoid this risk, use the real-time measuring of PCI utilization or throughput to immediately show when the bus gets idle.

#### **Combining Both Methods**

To utilize the advantages of both methods, proceed as follows:

- Run a benchmark and observe the PCI performance with the real-time measurements.

- Set up a post-processed analysis and reproduce the situation in which the performance dropped.

- Take the snapshot.

- Analyze the recorded data using the post-processed analysis.

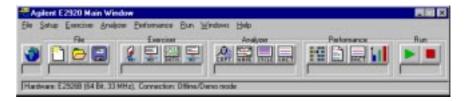

# The PCI Performance Optimizer's User Interface

The User Interface of the Agilent E2925B Opt. 200 Performance Optimizer is fully integrated into the framework of the Agilent E2925B Exerciser and Analyzer. All its windows and controls appear as additional features of the GUI that is assumed to be known from the PCI Exerciser and Analyzer software.

**Navigation**

The most important features of each part of the framework are available via the buttons in the respective button group. All these features and more are available via the menus of the main window, as well. As a third way, there are the overview windows provided by the user interface. These windows offer process-oriented access to the individual features.

**Performance Button Group**

The direct way to open the windows providing the features of the PCI Performance Optimizer is to click on the respective buttons in the *Performance* button group.

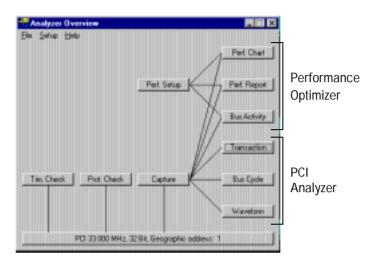

Overview Window

Both the PCI Analyzer and the PCI Performance Optimizer employ an internal trace memory, which is used to record the data traffic on the PCI bus. Therefore, they are both presented in one overview window. One way to open this window is to select *Show Analyzer Overview* from the Performance menu.

This Analyzer Overview window shows the individual components of the PCI Analyzer and the PCI Performance Optimizer and how they interact. Clicking the buttons brings up the respective windows.

**Performance Windows**

Within the PCI Performance Optimizer, there are the following windows provided for post-processed performance analysis and optimization:

### • Performance Setup

With the Performance Setup window you can set up the contents of the report to be generated, identify master and target devices to be considered in the test, and control the data capture for the performance analysis.

#### • Performance Charts

The performance charts show graphical representations of the performance-relevant aspects found in the captured PCI traffic.

### • Performance Report

The textual performance report lists all results in a hierarchical way, so you can focus on different levels of detail.

### · Bus Activity Lister

The bus activity lister summarizes all transactions found in the captured data. However, for each bus activity, only properties are displayed that are of interest in a performance analysis.

Real-Time Performance Measurements

Additionally, the PCI Performance Optimizer employs features for realtime performance measurements. These features are assumed to be known from the PCI Analyzer. For a short introduction, refer to "Determining the Overall System Performance" on page 17.

For detailed information refer to *Analyzing PCI Performance* in the "Agilent E2925B PCI Analyzer User's Guide".

## Rules for Proper PCI Design

When designing PCI devices a lot of design rules need to be obeyed to avoid your design conflicting with other devices. Furthermore, there are rules that need to be followed to improve the communication abilities of the devices. Making the devices behave according to these rules ensures that the device will not only work with good performance in a test environment, but on all platforms and under most circumstances.

Even when respecting all of these rules, the design with the best performance still depends on the type of the device and its dedicated tasks. Hence, a fair amount of design experience is likely to yield better results.

Within this text, only a few rules can be named that are essential for good performance:

- Implement extended PCI commands

- The following commands are optimized for certain types of data transfer and should be used instead of plain Memory Read/Memory Write (MR and MW) commands whenever possible:

- Memory Read Line MRL

- Memory Read Multiple MRM

- Memory Write and Invalidate MWI

- · Use long bursts

On most platforms read bursts should have a minimum length of 64 dwords to gain reasonable performance. Write bursts should have a minimum length of one cacheline.

- Use memory commands, avoid I/O commands

I/O commands can stress the processor. Although the PCI bus performance might not be directly affected, the usage of I/O commands reduces the performance of the whole system by using CPU time.

- · Minimize latency

Latency is referred to as the time between two events on the bus. Minimizing the latency means reducing the time between two events and, thus, speeding up the communication considerably.

PCI devices can insert wait cycles into transfers for different reasons. For example, a device can have no access to its resources because they are occupied or locked by another device.

Such wait cycles increase the latency and should, therefore, be avoided where possible.

These are only a few basic rules that should always be respected. More hints for identifying poor designs and for improving the performance are given in "Going Further Into Details" on page 71.

# Running a Sample PCI Performance Optimizer Session

The Agilent E2925B Opt. 200 Performance Optimizer provides all features needed to gain full insight into the performance of any PCI system and its communicating devices. There are several ways to evaluate the characteristic measures of the system under test. Basically, you can distinguish between real-time measurements—while the system is running— and a detailed post-processed data traffic analysis. An introduction to these approaches, explained on an easy example, is found in the following.

# Determining the Overall System Performance

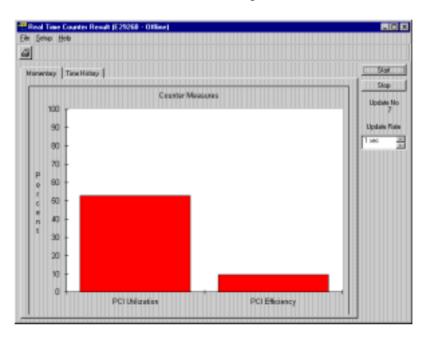

Using the real-time performance measures of the Agilent E2925B PCI testcard provides a very quick overview on the overall system performance. While the system under test is running, you can watch the values of a set of measures in two different views. For the measures to observe you can select four pre-defined variables like PCI efficiency or utilization. Alternatively, you can also define your own variables.

To run real-time measurements on the system under test, take the following steps:

1 Select *Real Time Counter Result* from the *Performance* menu of the application's main window.

The Real Time Counter Result window opens.

- **2** Press the *Start* button to the right.

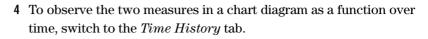

- By default, the two measures PCI Utilization and PCI Efficiency are displayed in percent. These values are re-calculated and displayed every second.

- **3** To change the update rate, use the arrow buttons next to the text field holding the current update rate.

NOTE In offline/demo mode, running the real-time measurements does not cause an error message but produces random values to be displayed.

The Available Measures

With the default settings, the Real Time Counter Result window displays two measures at a time. However, the application can employ up to six internal counters plus a reference counter that counts the clock cycles. These counters can be used to calculate any value of interest, whereas four can be displayed at a time.

For convenience, there are four pre-defined measures, that are commonly used when speaking of system or device performance:

- PCI Utilization

- PCI Efficiency

- PCI Throughput

- Retry Rate

How to set up the performance counters for your personal needs, is described in detail in the "Agilent E2925B PCI Analyzer User's Guide".

# **Analyzing the Performance of the PCI Host Bridge**

The Agilent E2925B Opt. 200 Performance Optimizer can be used to evaluate the performance of a particular device in the system under test. For this example, the PCI host bridge is observed while a master device is accessing the system memory through the host bridge.

For post-processed analysis, the data traffic on the PCI bus is recorded in the trace memory. The analysis on the stored data is done after the test has finished.

### Loading the Setup File

When preparing the Agilent E2925B Performance Optimizer for a test session you do not necessarily need to load a setup file. The setup file for the example measurements, however, is included in the software package. To set up your application for the example test, follow the instructions below:

- 1 Select *Load* from the *File* menu in the main window.

- **2** Select the file *perf.bst* in the path *samples/demo/*.

- **3** Click the *Load* button.

In case your application was not yet in performance mode, it will now switch to performance mode automatically. This causes the buttons in the *Performance* group and the items in the *Performance* menu to be enabled.

NOTE The setup file assumes an Agilent E2926A testcard to be used for the test—at least in offline/demo mode. If this is not the case, you will be informed in a message box. Change the configuration to the testcard required for the example.

## **Setting up the Measurements**

After you have loaded the setup file, the test measurements can be started. However, we need to verify the correctness of the settings. Therefore, we step through the setup and do changes where applicable.

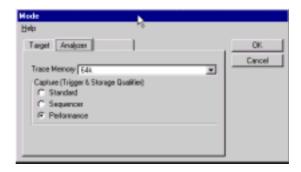

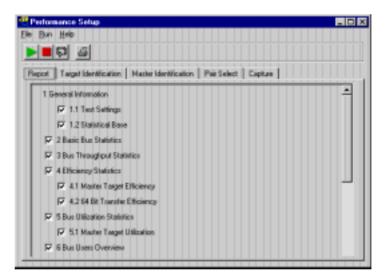

1 Select the *Performance Setup* item from the *Performance* menu.

The Performance Setup window opens, displaying the *Report* tab.

After the test has finished, the software provides a textual report of the results in the Performance Report window. With the items found on this tab of the Performance Setup window you can specify the particular results and statistics that are included in the report.

2 In our example, we leave all parts of the report included.

# **Specifying the Master and Target Identification**

In order to enable the Agilent E2925B PCI Performance Optimizer to identify particular devices communicating on the PCI bus, you need to specify them in the setup. Masters are identified by their GNT# lines, targets by their address range.

In the example, no particular masters are specified, because the complete traffic via the host bridge is to be observed.

- 1 If the Performance Setup window is not yet open, select *Performance Setup* from the *Performance* menu in the application's main window.

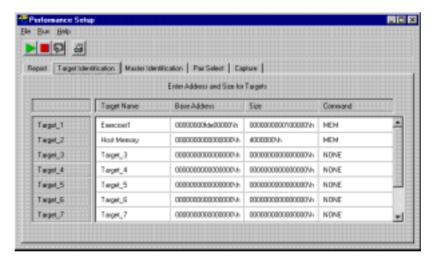

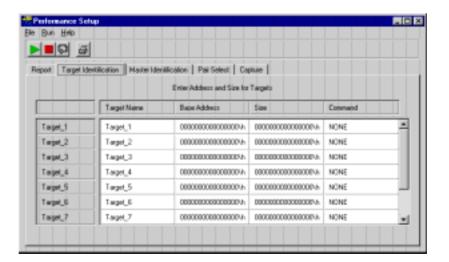

- **2** Switch to the *Target Identification* tab to see the view below.

In this table you can specify up to ten different target devices including their address ranges and the types of PCI commands that are considered in the measurements.

For the test example, two targets are explicitly specified in the table. On one hand there is the built-in target of a Agilent Exerciser card and on the other the host memory. Determining the Target Address

Range

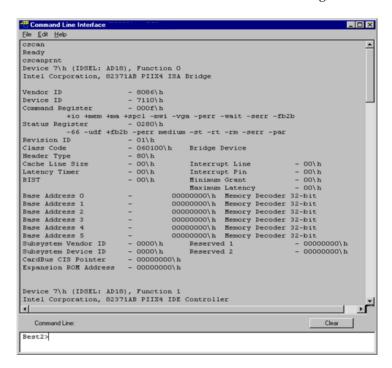

In case you need to know the address range of a particular target for the test setup, use the Command Line Interface:

- 1 Select *Command Line* from the *Window* menu in the application's main window to open the Command Line Interface window.

- 2 In the command line at the bottom of the window enter **cscan** and then **cscanprnt**, each followed by the return key.

These commands do a configuration scan on the PCI bus. The output area of the window now presents information on all devices that are found on the bus. This also includes the address ranges.

NOTE The Command Line Interface only works with a proper data connection to an Agilent Exerciser and Analyzer testcard plugged into the system under test.

The desired address ranges can now be entered in the *Target Identification* tab of the *Performance Setup* window.

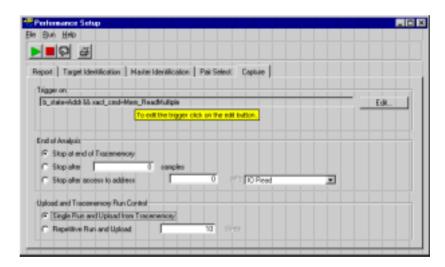

### **Specifying the Data Capture**

The setup of the performance test can not only be focussed on the traffic of particular devices, you can also control the start and the duration of the test. This implies both for the start and the end of the data recording, that you either can wait for a certain amount of time or for a particular event to happen on the bus.

- 1 If the Performance Setup window is not yet open, select *Performance Setup* from the *Performance* menu in the application's main window.

- **2** Switch to the *Capture* tab.

This tab is used to set up a trigger pattern for the start and additional conditions for the behavior of the software regarding the data capture.

In the test example, the data recording starts at the first occurrence of the PCI command **Memory Read Multiple**. The test stops as soon as the trace memory is completely filled with data.

### **Viewing the Test Results**

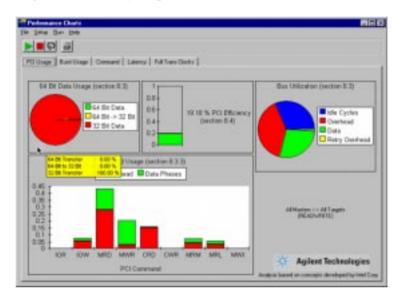

The results of the performance tests can be viewed in different ways. For instance, there is the Performance Charts window, that displays the test results in several graphical charts. Other ways are the textual report or the contents of the bus activity lister.

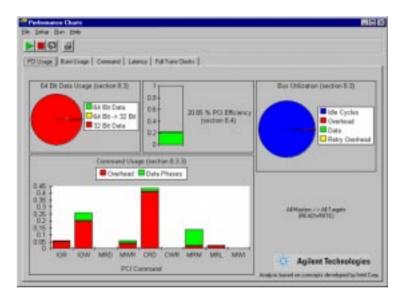

1 In the application's main window, select *Performance Charts* from the *Performance* menu, to open the Performance Charts window.

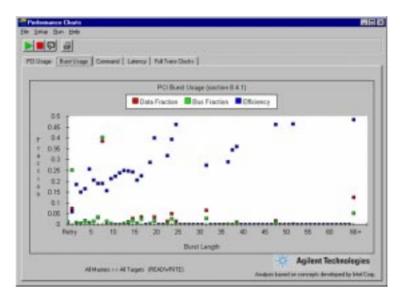

This window presents the performance of your system under test on five different tabs. The *PCI Usage* tab (as shown above) presents general traffic statistics like the bus utilization and the PCI command usage.

**2** Move the mouse over either pie chart to view the numerical values of the various pie slices.

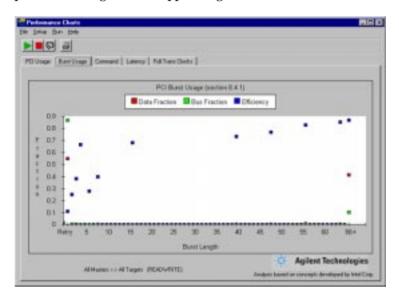

3 Switch to the Burst Usage tab.

This tab displays detailed information on the distribution of the data phases and the overhead over the different burst lengths in the traffic.

4 Switch through the different tabs to get an overview of the provided information.

**Loading the Example Test Results**

For convenience, the results of the example test also are included in the software package. To view these results, do the following steps:

- 1 In the Performance Charts window, select *Load* from the *File* menu. A message box appears, informing you that the selected action might take a few minutes to complete.

- **2** Click the *Continue* button to open the file dialog box.

- 3 In the file dialog box select the file perf.wfm in the path samples/demo/ and click the Load button.

After the loaded data is analyzed, the results are displayed in the Performance Charts window and the other windows of the Performance Optimizer.

NOTE This example waveform file was produced on a 64-bit system using an Agilent E2926B PCI testcard. Thus, to successfully load it into the GUI, the bus width and the hardware need to be set up the same way.

If your software is set up differently, a message box informs you. Change the hardware settings and repeat the procedure above.

# Setting Up a PCI Performance Optimizer Test

All steps that are required to set up a PCI performance test with the Agilent E2925B Opt. 200 Performance Optimizer are introduced here. It is explained how a proper setup is done, but not the use of the different features as such. See "Measuring System or Device Performance" on page 41 for information on the features.

The features of the Performance Optimizer are only available if the Performance Optimizer option has been installed with the correct license key.

Basically, you can divide the setup process into two parts:

- The hardware setup usually needs to be done only once for every system under test. It is assumed, that you already are familiar with the Agilent E2925B testcard. If you need to look up, how to install the testcard in the system under test and how to connect it to the control PC, refer to the "Agilent E2925B PCI Analyzer User's Guide".

The additional steps required for the Performance Optimizer are

- The **software setup** includes starting the Performance Optimizer—once per test session—and the individual setup for every single test. Information on these steps is found in "Preparing the Software for the Test" on page 30.

described in "Setting Up the Test Hardware" on page 28.

## Setting Up the Test Hardware

To evaluate a system's performance with the Agilent E2925B Opt. 200 Performance Optimizer, the Agilent E2925B testcard must be plugged into the system under test. Refer to *Possible PCI Analyzer Configurations* in the *Analyzer User's Guide* for the different possible configurations.

**Overall System Performance**

If you wish to test a system's PCI performance but not the performance of a particular PCI device on the bus, your hardware setup is already finished with the installation of the testcard and the establishment of the connection to the control software. Proceed with "Preparing the Software for the Test" on page 30.

**Performance of Particular Devices**

On the other hand, to evaluate the traffic of particular PCI devices, you need to allow the Performance Optimizer to identify these devices.

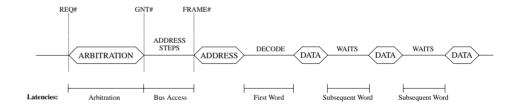

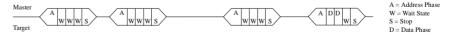

Master devices initiate all read/write traffic on the PCI bus. They request the bus from the arbiter, which grants the use of the bus to them when the bus is free. Master and arbiter use REQ# (request) and GNT# (grant) lines for communication. When the master's request is granted, it first puts an address on the bus. The address is then read and decoded by all target devices. The target that has the address space covering the address on the bus replies to the master, and the data transfer may start.

Thus, there are different ways of identifying the two different types of PCI devices:

- Master devices are identified by their GNT# lines. How to specify the

master devices and their GNT# lines in the Performance Optimizer is

described in "Master Identification" on page 29.

- Target devices are identified by their address spaces. How to specify the target devices and their address spaces is described in "Target Identification" on page 30.

### **Master Identification**

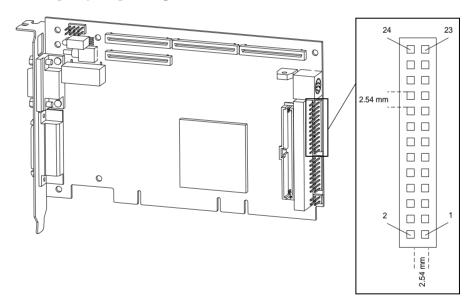

If you want to measure and evaluate the PCI traffic initiated by particular master devices, you need to set up the Performance Optimizer to identify these masters. For this purpose, the masters' GNT# lines must be made accessible to the Agilent E2925B Exerciser and Analyzer card. These lines must be connected to the external trigger input pins of the testcard—if necessary, by soldering a wire to it.

NOTE If you also want to run latency tests, the REQ# lines of the respective masters need to be connected to the testcard as well. It is advisable to do this now together with the GNT# lines.

The following figure shows the trigger lines of the Exerciser and Analyzer card. It indicates where to find the pins for the external trigger signals. "Setting up the Target Identification" on page 34 describes how to specify the pin assignment in the software.

### **Target Identification**

To identify the traffic to a particular target device no wiring is necessary. Every target in a PCI system gets a unique address range assigned to it during system startup. A target may have several decoders and may, therefore, use several different address spaces at once. The PCI Performance Optimizer considers the different address spaces of such PCI devices as independent devices.

The easiest way to find out the address ranges that the system under test assigns to the various target devices, is to use the Command Line Interface of the Agilent E2925B Exerciser and Analyzer. Open the Command Line Interface from the *Window* menu in the main window. To display a list of all installed targets, first enter the command *cscan* and then *cscanprnt*.

Basically, memory and I/O transactions can use the same addresses. Depending on the type of traffic to be examined, you can specify whether only memory commands, I/O commands, or both are to be evaluated by the PCI Performance Optimizer. See "Preparing the Software for the Test" on page 30 for more information.

# Preparing the Software for the Test

This section covers all information needed to set up the Agilent E2925B Opt. 200 PCI Performance Optimizer. It is assumed that the required hardware setup has already been done. If not, refer to "Setting Up the Test Hardware" on page 28.

The different steps of the software setup—except for the first one—can be done on the different tabs in the Performance Setup window of the GUI. This window can be opened either by selecting *Performance Setup* from the *Performance* menu or by clicking the Performance Setup button in the main window.

Steps of Software Setup The different steps of the software setup are:

• Enabling the Performance Optimizer.

Before you can program any test setup and run any test, you need to enable the PCI Performance Optimizer. How to do this is described in "Enabling the PCI Performance Optimizer" on page 32.

• Report tab.

The software will create a textual report on the evaluation results of the system under test. To set up this report for your individual needs, see "Setting Up the Report" on page 33.

• Master Identification tab and Target Identification tab.

In case you want to run performance measurements on particular PCI devices, you need to specify the respective master and target devices. This step is explained in "Setting up the Target Identification" on page 34.

• Pair Select tab.

To restrict the performance test on a single device or a single master/target pair, see "Selecting a Master/Target Pair" on page 36 for instructions.

• Capture tab.

Finally, to customize the start and end of the measurement period, you can specify trigger variables. See "Setting Up the Data Capture" on page 37 for details.

Once you have enabled the PCI Performance Optimizer, you can do your setup in any order you like.

### **Enabling the PCI Performance Optimizer**

The PCI Performance Optimizer is a software package that can be regarded as an add-on part of the PCI Analyzer. For this reason, it is also included in the Analyzer Overview window.

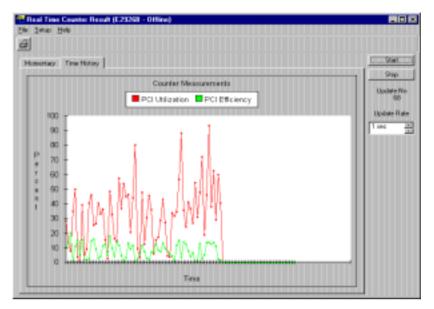

Performance measurements can only yield correct values if all bus cycles are evaluated and no filters set. However, when starting the Agilent E2920A software GUI, the analyzer mode *standard* is active by default. This standard mode allows to program a storage filter to omit unwanted bus cycles and is, therefore, of no use for performance tests. Thus, the analyzer mode needs to be changed.

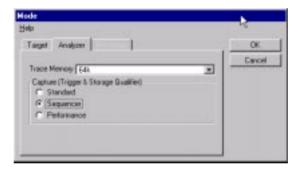

To enable the PCI Performance Optimizer, proceed as follows:

- 1 Select *Enable* from the *Performance* menu in the main window. A message box appears telling you, that you need to change the capture mode of the PCI Analyzer to *Performance*.

- **2** Click *OK* to open the Mode window.

- 3 In the Capture (Trigger & Storage Qualifier) group on the Analyzer tab, select Performance.

- 4 Click *OK* to close the Mode window again.

Now the items in the *Performance* menu are enabled as well as the buttons in the *Performance* group of the main window and in the Analyzer Overview window.

### **Setting Up the Report**

The Agilent E2925B Opt. 200 PCI Performance Optimizer creates a textual report with every test. This report contains general information, overall system performance, and detailed traffic statistics. It also contains hyperlinks for navigation between related topics in the report.

By default all available information will be included in the report. However, you can customize the contents of the report for your individual needs:

- 1 If the Performance window is not yet opened, click the Performance Setup button in the main window or the Analyzer Overview window.

- 2 Select the *Report* tab.

3 Check all topics that you want to have included in the report, uncheck those, that you want to omit.

With this selection, only those sections will appear in your report that are relevant for your test.

### **Setting up the Target Identification**

The PCI Performance Optimizer allows to evaluate the performance of single PCI devices or communicating pairs of devices. The target identification is used to specify the target devices of interest. Every target is identified by the address range that it decodes. You can monitor up to ten different targets at a time.

One target device in a PCI system may have up to six target decoders, each using its own address space. Within the Performance Optimizer they are regarded as independent targets.

NOTE If you need to know the address range of a target device, open the Command Line Interface (CLI) from the *Window* menu in the main window and enter the commands *cscan* and then *cscanprnt*, each followed by the return key. The CLI then lists all devices found on the PCI bus including their address spaces.

To define the target identification proceed as follows:

- 1 If the Performance window is not yet opened, click the Performance Setup button in the main window or the Analyzer Overview window.

- **2** Select the *Target Identification* tab.

- 3 If you wish to have a particular name for a target in the report and in the graphical displays, click into a *Target Name* field and enter a name. Alternatively, you can use the default name.

- 4 Click into the *Base Address* field of the same row and enter the base address of this target's memory. The ending \( \mathcal{h} \) marks hex values.

- 5 Click into the *Size* field of this row and enter the size of the target's memory. The ending \( h \) marks hex values.

- 6 Click into the Command field of this row and select one of the commands from the list. With this selection you can restrict your measurements to traffic using either I/O commands or memory commands, or ignore it at all.

- 7 Repeat the steps for all targets you want to be considered in the performance measurements.

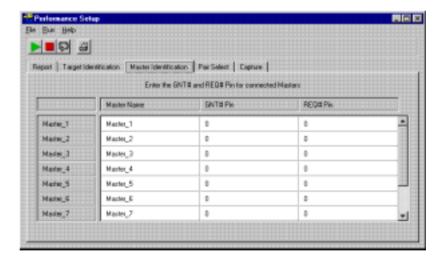

### **Setting up the Master Identification**

The master identification is used for performance measurements on one or more particular master devices. Every master is identified by its GNT# pin. You can monitor up to ten different masters at a time.

To define the master identification proceed as follows:

- 1 If the Performance window is not yet opened, click the Performance Setup button in the main window or the Analyzer Overview window.

- **2** Select the *Master Identification* tab.

- **3** If you wish to have a particular name for a master in the report and in the graphical displays, click into a *Master Name* field and enter a name. Alternatively, you can use the default name.

- 4 Click into the *GNT*# *Pin* field of this row and enter the trigger port number that this master's GNT# line is connected to. Zero (0) means not connected.

- 5 Click into the *REQ# Pin* field of this row and enter the trigger port number that this master's REQ# line is connected to. Zero (0) means not connected.

- If the REQ# pin of a master is not connected to any trigger port of the Agilent E2925B Exerciser and Analyzer card, arbitration considerations and latency measurements cannot be done for this master.

- **6** Repeat the steps for all masters you want to be considered in the performance measurements.

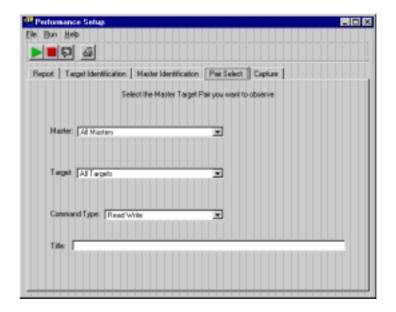

### Selecting a Master/Target Pair

Besides the more general performance measurements for the specified PCI devices, the Performance Optimizer can also report detailed transaction statistics for a particular device or a communicating pair of devices.

To select a device or a pair of devices for the test, proceed as follows:

- 1 If the Performance window is not yet opened, click the Performance Setup button in the main window or the Analyzer Overview window.

- 2 Select the Pair Select tab.

**3** From the *Master* list and the *Target* list select the combination of devices that you want to observe.

- 4 If you want to restrict your measurements to data transfers in one direction only, make the respective selection in the *Command Type* list.

- The traffic direction is defined as seen from the master's view. Thus, *Read* represents the traffic from target to master, and *Write* from master to target.

- 5 If you want to specify a title that represents the device selection, enter a title in the *Title* text field. This title will then appear in the report and the output charts.

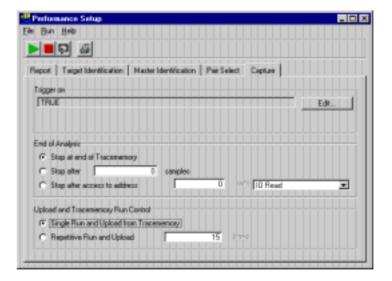

#### **Setting Up the Data Capture**

For certain tests it can be very useful to measure the performance during a particular period of time. Especially, if you want to optimize or debug a PCI device, it is required to record the data traffic for post-processed analysis only when certain events occurred.

For purposes like this, it is possible to either delay the start of the test for a fixed time or to wait for a trigger event on the bus. Also, the end of the test can be set to a fixed number of recorded bus clocks or after an access to a certain address with a certain command.

To specify a trigger for a conditional start, proceed as follows:

- 1 If the Performance window is not yet opened, click the Performance Setup button in the main window or the Analyzer Overview window.

- 2 Select the Capture tab.

**3** Specify the trigger in the *Trigger on* group by clicking on the *Edit* button.

The Capture window opens, where you can define the test to either start immediately or after the specified pattern was found to be true. This window should be known from the Agilent PCI Analyzer GUI and is not explained in detail here. If you need more information, please refer to *How to Set Up the Trigger* in the "Agilent E2925B PCI Analyzer User's Guide" Agilent.

- 4 Define the length of the test run in the *End of Analysis* group. The three possible options are:

- Stop at end of Tracememory (default).

With this option the measurements continue until the complete trace memory is filled. The size of the trace memory depends on the settings in the Analyzer tab of the Mode window, which is a feature of the Agilent E2925B PCI Analyzer. Performance measurements

of the Agilent E2925B PCI Analyzer. Performance measurements based on a larger amount of samples can be gained with the use of a Agilent E2995A 155 x 4M Trace Memory board.

- Stop after ... samples.

This option defines the test to stop after a certain number of recorded traffic samples. Specify the number of samples to record in the text field. This number must not be larger than the size of the trace memory.

A sequence of bus cycles without any signal changes concerning the performance (for example idle states) is stored as one sample. Thus, the number of observed bus cycles is larger than the number of samples in the trace memory.

- Stop after access to address  $\dots$  with  $\dots$

The analysis stops after an access to the specified address with the specified PCI bus command. Enter the address in hex format in the text field and select a bus command from the list.

If the address or command does not occur on the bus, the test will run until the trace memory is filled completely.

- 5 The bottom group in the *Capture* tab of the Performance Setup window features the *Upload and Tracememory Run Control*. You can select one of two options:

- Single Run and Upload from Tracememory (default).

With this option the performance test runs only once.

- Repetitive Run and Upload.

Select this option if you need a large amount of samples to gain more reliable measurement results. The statistical calculations are done on the accumulated values. Enter the number of test repetitions in the text field.

If the measurements should run too long, you can always manually terminate the tests. The results presented then are calculated on the completed test repetitions only.

NOTE If you store the waveform file after a repetitive test run, only the data of the most recent test will be stored. Later analysis of this file will possibly yield results other than the statistics on the complete set of tests.

# Measuring System or Device Performance

The Agilent E2925B Opt. 200 PCI Performance Optimizer can be used to measure the performance of a complete PCI system as well as to analyze particular PCI devices. The presented results and statistics allow to debug the test devices and to optimize their performance in terms of data throughput, efficiency, and bus utilization.

After you have set up the test correctly (as described in "Setting Up a PCI Performance Optimizer Test" on page 27), you can run it and, when finished, examine the results in several different views:

- All information needed to run the performance measurements is found in "Running the Performance Measurements" on page 42.

- After the test is finished, the Performance Charts window presents the results in a graphical manner on several window tabs. These charts are explained in "Interpreting the Result Charts" on page 43.

- An introduction to the contents of the performance report can be found in "Interpreting the Report Output" on page 48.

- An example of a performance report of a system evaluation test is explained in more detail in "Using the Report Output for Performance Evaluation" on page 50.

- Another example containing statistics on the data traffic of a particular device is found in "Using the Report Output for Performance Optimization" on page 55.

# Running the Performance Measurements

With the Performance Optimizer there are two ways how to evaluate the performance of the devices under test:

**Real-Time Measurements**

You can define up to four variables—or use pre-defined ones—that represent measurement values as bus utilization, efficiency, etc. With these variables a real-time measurement can be run, where you watch these values while the system is running. These test options can be found in the Performance menu of the application, although they are also possible with the Agilent E2925B PCI Analyzer only. For a description of real-time measurements, refer to the "Agilent E2925B PCI Analyzer User's Guide".

**Post-Processed Analysis**

The other option is to record detailed information on the bus traffic in the trace memory and evaluate them after the test is finished. This approach is called post-processed analysis and is explained here.

Assuming a proper test setup is made, the test will record bus traffic information in the trace memory for a certain amount of time. This length depends on the system speed and the size of the trace memory. The test run can be controlled with several buttons found in the different windows of the Performance Optimizer—except the Performance Report window.

Start the Test

In order to start the test, click on the Run button in either of the windows of the Performance Optimizer. You can also select Run from the Performance menu in the main window.

Stop the Test

If for any reason your test does not seem to finish within a reasonable time, for example the specified trigger event does not occur, you can terminate it manually. Click the Stop button in either of the windows of the Performance Optimizer or select *Stop* from the Performance menu in the main window.

After the test finished, the contents of the trace memory will be evaluated and the results will be presented in the Performance Charts window, the Performance Report window and the Bus Activity Lister window.

Rescan the Trace Memory

The Rescan button is thought to be used when doing different performance calculations on the same data. For example, if you want to compare the performance of different master-target pairs during the same test period. In a case like this you do not want to run a new test but to evaluate the data in the trace memory again with different settings. After running the test for the first master-target pair, you only have to change the selected pair in the setup window and click on the *Rescan* button to calculate the new results.

## **Interpreting the Result Charts**

After successfully running the performance measurements on the system under test, you can view the results in the different windows of the Performance Optimizer. Here a description to the charts of the Performance Charts window is found.

These charts display several results of the analysis. These results always refer to the device pair specified in the test setup. If you want to evaluate the performance of the complete system under test, the device pair All Masters/All Targets needs to be selected. For more information see "Selecting a Master/Target Pair" on page 36.

**Performance Chart Tabs**

The result charts in the Performance Charts window are located on five different window tabs:

- "PCI Usage" on page 44.

- "Burst Usage" on page 45.

- "Command" on page 46.

- "Latency" on page 47.

- "Full Transaction Clocks" on page 48.

**Data Source for Performance Charts**

All performance charts are derived from the data recorded in the trace memory. The complete results of the measurements on that data are presented in the performance report. To view all details concerning a certain performance chart refer to the respective section in the performance report.

#### **PCI Usage**

This tab displays general statistics on the usage of the PCI bus. It contains up to four charts—depending on the test setup—that provide information on the recorded bus traffic: 64-bit data usage, PCI efficiency, bus utilization, and command usage. The selection of the master-target pair observed in the test is displayed in the lower right corner of the window.

For a detailed description of the charts, see the topic named *PCI Usage Tab* in the online help. The contents of the different charts are explained in the respective sections of the performance report.

Depending on the test setup, up to four diagrams are shown in this overview.

### **Burst Usage**

The diagram in this tab corresponds to the section 8.4.1 of the performance report. It shows the distribution of the burst lengths that contributed to the bus traffic. Burst lengths are displayed up to 65, where the length is the number of address phases plus the number of data phases. All longer bursts appear together as 66+.

For a detailed description of the chart, see the topic named *Burst Usage Tab* in the online help.

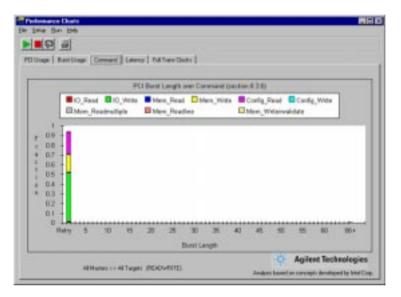

#### Command

The diagram in this tab corresponds to the section 8.3.6 of the performance report. It displays the distribution of the different bus commands during the traffic (compare the "PCI Usage" on page 44). More specifically, it is splitted up with respect to the different burst lengths. Burst lengths are displayed up to 65, where the length is the number of data phases. All longer bursts appear together as 66+.

For a detailed description of the chart, see the topic named Command Tab in the online help.

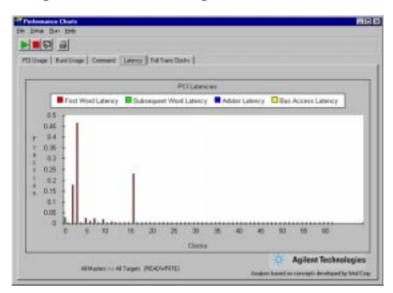

#### Latency

The diagram in this tab corresponds to the section 8.6 in the performance report. It resolves the distribution of the different latencies that occurred during bursts of the different lengths.

For a detailed description of the chart, see the topic named  $PCI\ Usage\ Tab$  in the online help.

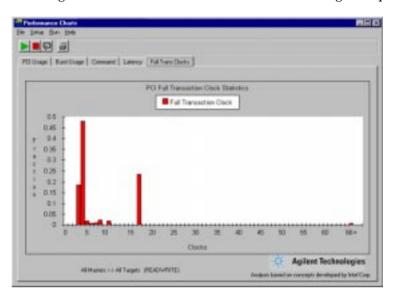

#### **Full Transaction Clocks**

The diagram in this tab shows the distribution of the total lengths of transactions that were used for the communication between the selected master and target. Total length means the total number of bus cycles including wait states. The sum of all fractions in this diagram equals one.

For a detailed description of the chart, see the topic named *PCI Usage Tab* in the online help.

## **Interpreting the Report Output**

After data traffic from the PCI bus was recorded in the trace memory and the performance measurements were done on this data, the Performance Report window displays the results in a textual report. To open this window click the Performance Report button in the *Performance* group of the main window.

The Report as Chart Reference

The report contains detailed performance information and traffic statistics. A selection of these results is also presented in several charts in the Performance Charts window. The corresponding section of the report is displayed as a reference with the diagrams. See "Interpreting the Result Charts" on page 43 for more information.

**Reduced Report Contents**

You can choose which parts of the report are shown or omitted before starting the measurements. For this purpose go to the *Report* tab (see "Setting Up the Report" on page 33) in the Performance Setup window. This window opens, for example, when selecting the Setup Window item from the Setup menu in the Performance Report window.

Navigation in the Report

For convenience, the report is structured in several sections. The first sections present an overview on the performance of the complete system under test. Then there is general information on the performance of the specified master and target devices. The last sections contain detailed statistics on the communication between the selected device pair.

Hyperlinks—marked with blue text—are provided in several places in the report. They connect report sections with related subjects. Clicking a link leads you to the section describing the performance value in more detail.

To go back to the previously viewed section click the Back button in the tool bar of this window.

**Report Contents**

To learn about the contents provided in the various sections of the report, you can

- work through the "Using the Report Output for Performance Evaluation" on page 50. This example describes the sections 1 to 7.

- work through the "Using the Report Output for Performance Optimization" on page 55. This example describes the section 8.

- see the "Report Reference" on page 81 for a complete and detailed reference of the contents.

## Using the Report Output for Performance Evaluation

This example shows how the report sections 1 to 6 can be used to evaluate the performance of a PCI system or device.

For this example, a graphics card was used as device under test in a 32-bit system and a computer game as a benchmark. When running the benchmark, it seems that the game runs too slowly. Therefore, the PCI performance was examined using the PCI Performance Optimizer. The report sections that lead to the graphics card's shortcomings, are shown and explained in the following. Some of the report sections can also be viewed in charts.

Note, that current PC generations usually use AGP graphics cards instead of PCI graphics cards, because they often interfered with other PCI devices.

#### General Information on the System under Test

The first section in the test report is titled **General Information** and lists the bus speed and all specified devices. The example device in this test is the target device named **Graphics** as displayed in the figure below:

The data traffic to the graphics card is part of the bus traffic and is analyzed in the following report sections.

#### **Analyzing the PCI Throughput**

The second report section displays the basic bus statistics. Here values like PCI throughput, bus utilization and efficiency are presented.

Compare the overall PCI throughput in the basic bus statistics to the throughput in the bus throughput statistics (report section 3).

The table shows that no other target was involved in the data traffic. Due to the benchmark, the graphics card was the only device using the PCI bus. No other activities took place while the capture was taken.

The measured throughput of 0.9535 MByte/s seems to be the reason for the poor performance. The PCI bus supports 132 MBytes/s peak transfer rate. Therefore, a way for improving the data throughput to the graphics card must be found.

#### Analyzing the PCI Utilization

In the basic bus statistics (report section 2), you can find the PCI utilization among others.

The **PCI Utilization** value is 50.07 %. This means that the bus was used only in about half of the available clock cycles. During the remaining time it was idle.

Now compare the PCI Utilization to the Non-retry Utilization. The latter is the bus utilization without retries. Only 3.60 % of the bus cycles were used for data traffic without a retry. This means that the bus was mainly occupied by transporting retry overhead.

A more detailed analysis of the bus utilization can be found in the bus utilization statistics (report section 5):

From this table, it can be seen that the bus mainly is occupied by retries  $(46.47\,\%)$  and that the graphics card basically is the only target that used the bus during the measurement:  $50.04\,\%$  compared to a total utilization of  $50.07\,\%$ .

#### **Analyzing the PCI Efficiency**

Within the basic bus statistics (report section 2) you can see the values for the PCI Efficiency and the Non-retry PCI Efficiency of the system under test during the measurements.

An efficiency of 1.44 % is very little, especially if there are not many devices requesting the bus concurrently. The Non-retry PCI Efficiency value only takes successful transfers into account and neglects the retries. But this value of 20.09~% still is very poor. Usually, a value of about 50~% is considered to be a reasonable efficiency value.

To go further into details, see the efficiency statistics (report section 4).

These statistics show a good PCI Byte Enable Efficiency value of nearly 100 %. This means, that transfers used the full bus width in most cases. Therefore, it is impossible to improve the card behavior with respect to this property.

On the other hand, the analysis of the retry behavior confirms what has already been seen when analyzing throughput and utilization:  $18.66\,\%$  retry overhead is very much.

NOTE When testing a 64-bit system, an additional section is included in the report for efficiency analysis of 64-bit transfers. For more information please refer to "Efficiency Statistics (Report Section 4)" on page 88.

#### The Bus Users Overview

In report section 6 the Bus Users Overview is displayed. This list leads to the device pair being responsible for the poor performance results.

The Bus Users Overview table contains indices that rate the performance of a device pair. Normally, you can compare the values of the several devices. In this case, however, a direct comparison is not possible because there is not enough traffic from other devices included for reasonable values.

| 6 BUS USERS OVERV | 6 BUS USERS OVERVIEW              |  |  |  |  |

|-------------------|-----------------------------------|--|--|--|--|

| Calculated as     | Utilization divided by Efficiency |  |  |  |  |

|                   | All Masters                       |  |  |  |  |

| Graphics          | 34.68                             |  |  |  |  |

| Other Target      | 0.02                              |  |  |  |  |

| All Targets 34.70 |                                   |  |  |  |  |

The Bus Users Overview index is calculated as utilization divided by efficiency. High utilization and low efficiency result in a high index value. This means, that small values indicate good performance. A value of around 1 is good. The graphics card's index is 34.68, which is far too high.

Finally, the report section 7 deals with interrupt statistics and is not relevant for the considerations in this sample walk through.

#### Summary for the Performance Evaluation Example

After the report sections 1 to 6 have been analyzed, the performance evaluation results in:

- the bus being used almost only by the graphics card,

- the graphics card using the bus only to the half of its capability,

- the graphics card using the bus mainly to transport retry overhead,

- the graphics card having a poor index in the "Bus Users Overview"

It is obvious that the graphics card should be improved or replaced, for example, by an AGP card.

# Using the Report Output for Performance Optimization

This example explains how the flaws of a particular PCI device can be examined and how to find ways to improve its design. It is assumed that a general evaluation of the system's performance and behavior already was done and the device with the poor performance was identified.

To gain this general overview on the system under test, please refer to the "Using the Report Output for Performance Evaluation" on page 50. There, the basic bus metrics PCI Throughput, PCI Utilization, PCI Efficiency, and the Bus Users Overview are evaluated with help of the respective sections of the performance report. The result is that the examined graphics card in the system under test shows a very poor performance and should be replaced.

From the report sections 1 to 6, it was derived that the retry behavior of the card is the reason for the poor PCI performance. In order to improve the PCI design of the card, the card's traffic behavior must be analyzed in more detail.

For this purpose, the report section 8 will be analyzed during this example. The used system under test still is the same as in the other example. Section 8 lists detailed statistics about the communication between the specified master-target pair, in this case the traffic between the graphics card and **All masters**.

#### **Analyzing the Bus Utilization**

The retry behavior of the graphics card was identified as the reason for poor performance. Therefore, the analysis of the bus utilization is useful. Report section 8.3 provides the results for the selected master target pair:

The **Sum of Utilization** indicates how intensively the selected device pair participated in the whole traffic on the PCI bus. Here, 50.04 % of all sampled clocks were used by this device pair.

Furthermore, this analysis indicates a remarkable retry overhead (46.47 %). However, it should be taken into account that only the traffic between graphics card and its master, the PCI bridge, was analyzed.

### **Analyzing the Traffic Overhead**

In this step it is examined, whether the master or the target device is responsible for the retry overhead. For this purpose, see the Time Overhead summary (report section 8.3.2). The time overhead analysis breaks down the values of the section 8.3. It points to the causes of the overhead, and it shows what type of overhead occurred.

| 8.3.2 Time Overhead             |                 |            |              |

|---------------------------------|-----------------|------------|--------------|

| Average Decode Speed (1 == fast | ) 2.00 cycle(s  | s)         |              |

|                                 | Overhead car    | used by    |              |

|                                 | Master   Target | Both       | Sum          |

|                                 |                 |            |              |

| a) Address Phase                | 1.46 %          |            | 1.46 %       |

| b) Waits                        | 0.00 %   1.46 % | %   0.00 % | 1.46 %       |

| 1) First Word Latency (a+b)     | 1.46 %   1.46   | %   0.00 % | 2.92 %       |

| 2) Retry Transactions           | 94.22           | 8          | 94.22 %      |

| 3) Subsequent Latency           | 0.00 %   2.85   | %   0.00 % | 2.85 %       |

| Sum ((1) + (2) + (3))           | 1.46 %   98.54  | *   0.00 % | <br>100.00 % |

The average address decode speed of 2 clock cycles is all right and does not necessarily limit the performance.

The sum of all different overhead types is always  $100\,\%$  and corresponds to the time overhead value found in report section 8.3. Out of this total traffic overhead, the master caused only  $1.46\,\%$ . The graphics card (target), on the other hand, caused  $98.54\,\%$ . It is obvious that the graphics card is responsible for the poor performance. The reason for the overhead is obvious as well:  $94.22\,\%$  of the total overhead is caused by target retries.

To improve the performance of the graphics card, retries must be eliminated. Reasons for retries could be, for example, that the target's components are too slow, or that it has problems with its resources or memory.

Furthermore, it is remarkable that the target causes overhead by inserting initial waits  $(1.46\,\%)$  and subsequent waits  $(2.85\,\%)$ . However, this is insignificant compared with the huge overhead caused by retries. It indicates that an examination of the inserted waits could help to find further ways of improving the device.

#### **Analyzing the Wait States**

To analyze the source for the wait states during the communication, see the **Wait Histogram** (report section 8.3.5):

| 8.3.5 Wai | t Histogram |         |

|-----------|-------------|---------|

| Waits     | Master      | Target  |

| 0         | 50.00 %     | 0.00 %  |

| 1         | 0.00 %      | 2.75 %  |

| 2         | 0.00 %      | 3.47 %  |

| 3         | 0.00 %      | 43.77 % |

| 4         | 0.00 %      | 0.00 %  |

| continu   | ıed         |         |

Every wait sequence that was inserted by one device—either master or target—is counted as a wait sequence of length zero for the other device. Therefore, all wait sequences appear in both columns. As a result the sum of both columns equals 50 %. The closer the value in the first row reaches 50 %, the less wait sequences this device has caused.

In this case, the table shows, that no wait states are inserted by the master. The target, however, inserted sequences of wait states, mainly three clocks long. These are probably waits inserted when performing retries. The target should be examined to see whether it can be prevented from performing retries.

## Analyzing the Byte Enable and Burst Behavior

This step examines the byte enable and burst behavior of the graphics card in order to find further ways for improvements.

The detailed analysis of the Byte Enable Efficiency shows that almost always the maximum of 4 bytes per data phase was transferred. This has been detected earlier in the bus statistics analysis in report section 4 (see "Analyzing the PCI Efficiency" on page 53 for details).

This shows a good PCI design of the master device, in this case, the motherboard's PCI bridge. It initiates write transfers to the graphics card and puts the data on the bus. The graphics card, as being the target, has no influence on the distribution of byte enables.

Now, regard the average burst length in the data communication of the selected device pair. For this purpose, see the report section 8.3.1:

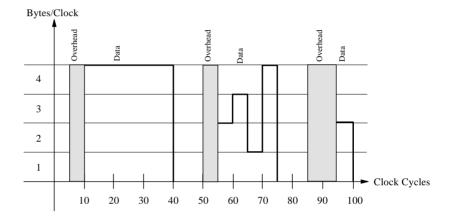

As the diagram shows, the average burst length is only 1 data phase. Basically, the longer the bursts are, the better the performance. Their length is limited by the capabilities of the participating devices. Thus, this average burst length indicates very poor design and is a root cause for poor performance. The burst length depends on the behavior of both master and target and should, therefore, be analyzed in more detail.

### **Analyzing the Bursts**

Proper PCI design results in the devices being capable of performing burst lengths greater than 1. Because the average burst length in our case is only 1, it is obvious that the graphics card under test cannot handle bursts properly.

A detailed list of the different PCI bus commands used with bursts of a particular length is found in report section 8.3.6:

| 8.3.6 | 8.3.6 Burst Length over Command |        |        |         |        |        |        |        |            |

|-------|---------------------------------|--------|--------|---------|--------|--------|--------|--------|------------|

| Brst  | IO_REA                          | IO_WRI | MEM_RE | MEM_WR  | CONFIG | CONFIG | MEM_RE | MEM_RE | MEM_WR     |

| Len   | D<br>                           | TE<br> | AD<br> | ITE<br> | _READ  | _WRITE | ADMULT | ADLINE | ITEINV<br> |

| 0     | 0.00 %                          | 0.00 % | 0.00 % | 94.18 % | 0.00 % | 0.00 % | 0.00 % | 0.00 % | 0.00 %     |

| 1     | 0.00 %                          | 0.00 % | 0.00 % | 5.82 %  | 0.00 % | 0.00 % | 0.00 % | 0.00 % | 0.00 %     |

| 2     | 0.00 %                          | 0.00 % | 0.00 % | 0.00 %  | 0.00 % | 0.00 % | 0.00 % | 0.00 % | 0.00 %     |

| 3     | 0.00 %                          | 0.00 % | 0.00 % | 0.00 %  | 0.00 % | 0.00 % | 0.00 % | 0.00 % | 0.00 %     |